Benutzer-Werkzeuge

Seitenleiste

Diese Seite zum Buch hinzufügen

Diese Seite aus Buch entfernen

Inhaltsverzeichnis

Anti-Aliasing-Filter für Delta-Sigma ADCs

(23.1.2017)

Ausgangspunkt

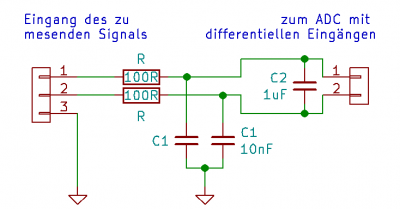

Angeblich ist einer der größten Vorteile eines Delta-Sigma-ADCs der, dass er einen verhältnismäßig einfachen analogen Anti-Aliasing-Filter benötigt. Es wird in den üblichen Application Notes immer nur von einem einfachen RC-Filter 1. Ordnung gesprochen.

Problematik

Sieht man sich jedoch eine exemplarische Übertragungsfunktion des dem Modulator nachgeschalteten Dezimationsfilters an, so kommt man ganz schön ins Staunen.

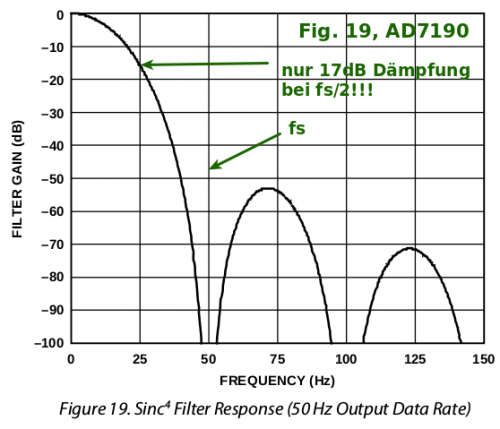

Am Beispiel des AD7190 wollen wir hier die Problematik diskutieren.

Master-Takt ist 4.92MHz, die Modulator-Abtastrate liegt bei einem 16-tel, also bei ca. 300kHz. Die Empfehlung lautet nun normalerweise, dass der analoge Tiefpassfilter bei eben dieser Frequenz eine entsprechende Dämpfung haben muss. Nehmen wir ein Störsignal mit einer Amplitude von -60dB_FS an, also 1/1000 des Messbereichs. Bei 5V Referenzspannung entspricht dies also 5mV.

Wir streben eine Rauschunterdrückung auf -150dB an, um noch etwas Reserven zu haben. Denn 22 Bit entsprechen ca. 132dB Dynamikbereich, den wir uns von Störern außerhalb unseres Nutzfrequenzbereichs nicht verschlechtern lassen wollen.

Nehmen wir nun weiters an, wir wollen unser Signal mit 50Hz abtasten, sind also an dem Frequenzbereich zwischen 0 und ca. 10Hz interessiert.

Ohne Chopping

Man traut seinen Augen nicht, wenn man hier nun sieht, dass der ADC bei fs/2 eine Dämpfung von nur 17dB hat. Hat man z.B. ein Störsignal von 5mV bei 30Hz, sieht man dies Signal mit -(60 + 25) = -85dB, das sind dann 280uV, auf einer scheinbaren Frequenz von 20Hz wieder!

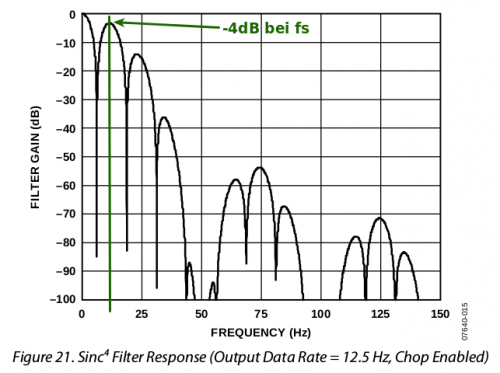

Mit Chopping

Mit chopping ergibt sich ein noch dramatischeres Bild, da man hier nun bei fs ein lokales Maximum in der Übertragungsfunktion hat, das eine Dämpfung von nur 4dB hat! D.h. alle Störer bei der Abtastfrequenz schalgen sich fast ungedämpft auf 0Hz, was bei quasistatischen Messungen wie Wägeprozessen fatal ist.

Ist chopping aktiviert, sollte man nie und nimmer mit 50Hz abtasten!

Abhilfe

Umgehen kann man dieses Problem, indem man den ADC so schnell wie möglich laufen lässt, einen passenden analogen Tiefpassfilter verwendet und den Dezimierungsfilter selbst und dafür sauber implementiert. Das erfordert natürlich einen gewissen Rechenaufwand und eine entsprechende Hardware.

Schnelle Abtastung

Unser ADC schafft max. 4800Hz Ausgangsdatenrate. Möchte man den Sinc-Filter 4. Ordnung und Chopping verwenden, kommt man nur mehr auf max. 1200Hz.

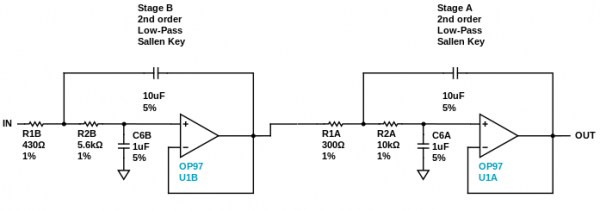

Analoger Tiefpassfilter

Setzt man die Grenzfrequenz des Filters bei 60Hz an, so hat man genau eine Dekade zwischen der Grenzfrequenz und der halben Abtastfrequenz (600Hz), bei der wir min. 90dB Dämpfung haben möchten, um mit dem angenommenen Störsignal von -60dB auf weniger als -150dB Störsignal zu kommen. Um das zu erreichen, braucht es einen Filter 5. Ordnung (20dB/Dekade und Ordnung). Das lässt sich nur mit hohem Aufwand betreieben.

Als Empfehlung für analogen Filterentwurf sei hier der Filter Wizard von Analog Devices angeführt:

http://www.analog.com/designtools/en/filterwizard/

Reduziert man die Anforderung, z.B. mit einer Grenzfrequenzreduktion auf 20Hz, so kommt man mit einem Bessel-Filter 4. Ordnung aus.

Je nach Anwendung kann solch ein aktives Filterdesign wieder unerwünschte Nebeneffekte wie Rauschen, Offset und Offsetdrift mit sich bringen.

Digitaler Dezimierungsfilter

Um nun noch die Abtastrate von 1200Hz auf 50Hz zu reduzieren, braucht es digitale Tiefpassfilter.

Hierfür kann ich den „Filtuino“ Filtergenerator empfehlen: http://www.schwietering.com/jayduino/filtuino/

Leider kann dieser keine Biquad-Strukturen erzeugen, welche die beste Möglichkeit sind, das Quantisierungsrauschen der digitalen Filter zu reduzieren. Das ist jedoch ein Punkt, den man vermutlich leicht verschmerzen kann.

Den Dezimierungsfaktor 600/50 = 12 würde ich mit 3 Stufen realisieren: 3x2x2. D.h. es braucht Filter mit einer Grenzfrequenz von je fs/12, fs/8, fs/8, in Hertz ausgedrückt sind das dann 600/12 = 50Hz, 200/8 = 25Hz, 100/8 = 12.5Hz.

Man hat somit immer genau eine Oktave zwischen Grenzfrequenz und der halben, neuen Abtastfrequenz. Hier würde ich eine Dämpfung von 90dB anstreben, was sich mit 3-stufigen Filtern je 5. Ordnung realisieren lässt (ein Filter 1. Ordnung hat -6dB/Oktave Dämpfung).

Zusammenfassung

Die Delta-Sigma ADCs halten nicht ganz das was sie versprechen - Anti-Aliasing-Filter mit einem einfachen RC-Filter. Dafür sind die Dezimierungsfilter zu schwach bzw. falsch ausgelegt. Doch dies zu umgehen ist nicht einfach und bringt neue Schwierigkeiten mit sich. Evt. würde die beste Lösung ein integrierter Delta-Sigma-Modulator in Kombination mit einer hochperformanten digitalen Hardware zur Abtastratenreduktion sein - denn das Verschieben des Quantisierungsrauschens hin zu hohen Frequenzen passiert im Modulator, welcher diesen hohen Auflösungsgewinn durch Überabtastung erst ermöglicht.